BAST (2021-02-16)

원제 : A SPACE-EFFICIENT FLASH TRANSLATION LAYER FOR COMPACTFLASH SYSTEMS

0. 개요

플래시 메모리는 낮은 전력 소비율과 충격 저항성에 의해 모바일 가전 제품의 비휘발성 스토리지로서 더 중요해지고 있다.

그러나 쓰기 전 지우기 작업이 수행되어야 하고, 지우기 작업이 쓰기 보다 큰 단위에서 수행된다는 기술적인 문제가 있다.

이러한 기술적 난관을 해결하기 위해 FTL이라 불리는 중간 소프트웨어 계층을, 일반적으로 호스트 시스템에서 플래시 메모리의 물리적 주소로 논리적 주소를 리디렉션 하기 위해 사용

기존 접근 방식은 쓰기 단위(페이지) 또는 지우기 단위(블록)의 세분화에서 이 주소 변화를 수행

본 논문은 주소 변환에서 두 가지 서로 다른 세분성을 결합한 새로운 FTL 설계를 제안

이는 coarse grain(블록 매핑을 의미) 주소 변환이 번역 정보를 유지하는데 필요한 자원을 감소시킨다는 아이디어에서 비롯됨

-> 비용과 전력 소비면에서 모바일 제품이 중요

반면 fine grain(섹터 매핑을 의미) 주소 변환은 작은 쓰기의 처리를 처리하는데 효율적

--> 거칠다, 덩어리지다 는 보통 블록 매핑이라고 먼저 생각해볼 것

--> 미세하다 등은 섹터로

추적 기반 시뮬레이션(trace-driven simulation)을 기반으로한 성능 평가는 제안된 체계가, 이전에 제안된 접근 방식을 크게 능가한다는 것을 보여줌

Index Terms - Flash memory, NAND-type flash memory, FTL, CompactFlash, address translation.

1. INTRODUCT

최근에 모바일 컴퓨팅 기기가 큰 인기를 끌고있으며, 이러한 모바일 장치는 소형, 경량, 저전력, 충격 저항 등 다양한 설계 요건을 강요한다.

이러한 요구사항은 기본 컴퓨터 시스템의 다양한 요소들의 재설계를 필요로 한다.

특히 모바일용 비휘발성 스토리지 하부시스템 설계는 기존 자기디스크가 기계적 특성으로 인해 전력 효율성과 내충격성이 전반적으로 부족하기 때문에 까다로운 분야 중 하나이다.

플래시 메모리는 작은 크기, 내충격성 및 낮은 전력 소비량에서 모바일 컴퓨터의 매력적인 장기 스토리지 미디어로 인식되고 있음

또한 기계적 지연이 수반되지 않기 때문에, 랜덤 엑세스가 가능하여 우수한 성능을 제공

이러한 속성은 하드 디스크를 에뮬레이트하는 플래시 메모리 기반 스토리지 서브시스템을 모바일 컴퓨터의 보조 스토리지로 인기 있게 만든다. (ex. CompactFlash, SmartMedia)

플래시 메모리의 용량이 증가함에 따라, 플래시 메모리의 사용이 더욱 보편화되어 기존 컴퓨터 시스템에서도 하드 디스크와 공존하거나 하드 디스크를 완전히 교체할 것으로 예상

그러나 플래시 메모리는 몇 가지 특성으로 인해 자기디스크를 쉽게 교체하기 어렵다.

1) 플래시 메모리에 쓰기 전에 지우기 작업이 선행되어야 하며, 쓰기 작업보다 크기가 더 커짐

2) 지우기 작업은 쓰기 작업보다 더 큰 단위에서만 수행 가능함

-> 단 하나의 바이트라도 업데이트하려면 많은 양의 데이터를 복원 뿐만 아니라 지우기 작업을 필요로함

잠재적 성능 저하 뿐만 아니라 전원이 예기치 않게 꺼질 경우 데이터 손실로 인한 무결성 문제가 발생할 수 있음

휴대용 장치에서 자주 발생할 수 있음

이러한 문제를 해결하기 위해 호스트 어플리케이션과 플래시 메모리 사이에 FTL이라는 중간 소프트웨어 계층을 사용

FTL은 호스트에서 각 쓰기 요청을 미리 지워진 플래시 메모리의 빈 위치로 리디렉션함

이 기술은 쓰기 전 지우기 제한 사항을 보완하지만, 빈 위치를 준비하는 추가 플래시 메모리 작업 비용가 주소 변환 정보를 유지하기 위한 추가 스토리지 비용이 발생하며, 그 양은 알고리즘에 따라 달라짐

본 논문에서는 대용량 스토리지 CompactFlash 시스템을 목표로하는 새로운 FTL 설계를 제안

제안된 FTL의 주요 동기는 거친 곡물 주소 변환이 관리 오버헤드를 낮추는 반면, 미세 곡물 주소 변환은 작은 크기의 쓰기를 처리하는데 효율적

제안된 체계는 두 가지 세분성을 결합하여 페이지 레벨 주소 변환의 스토리지 오버헤드를 줄이면서, 블록보다 작은 쓰기 요청을 효율적으로 처리할 수 있도록 한다.

또한 예기치 않은 정전에도 불구하고 플래시 메모리에 저장된 변환 정보의 일관성을 보장하는 방법을 제안

제안된 계획은 플래시 메모리의 전용 영역에 있는 변환 정보의 증분 업데이트(on incremental updates)를 기반으로 함

단일 원자 플래시 메모리 쓰기 작업에서 호스트 요청을 처리하는데 필요한 변환 정보의 여러 업데이트를 수행하여 변환 정보의 일관성을 달성

제안된 체계는 사용자가 시스템을 자주 켜고 끄는 소비자 장치에서 중요한 기능인 짧은 부팅 시간을 갖는 이점이 있음

논문 순서

플래시 메모리에 대한 개요를 제공하고 플래시 메모리 관리의 이전 접근 방식을 조사

제안된 체계에 대한 자세한 설명

추적 기반 시뮬레이션을 기반으로 한 이전 체계와, 제안된 체계의 성능을 비교

결론 도출

2. BACKGROUND

플래시 메모리는 시스템 내 프로그래밍을 허용하는 EEPROM의 버전

플래시 메모리에서 데이터는 일련의 프로그래밍 명령과 데이터 주소를 플래시 메모리 칩에 실행하여 작성

저장된 데이터는 전원이 꺼진 후에도 유지되므로 비휘발성 저장 매체로 사용 할 수 있으며, 크기가 작고 전력 소비가 적은 모바일 소비가 기기에 사용 가능함

플래시 메모리는 랜덤 방식으로 엑세스 할 수 있다는 장점이 있으므로 고성능을 발휘할 수 있음

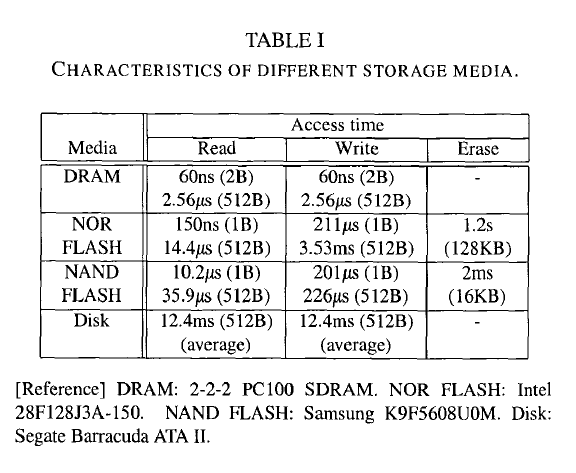

표 1은 플래시 메모리의 두 가지 주요 유형(NAND, NOR)을 포함한 다양한 스토리지 미디어의 특성을 비교

두 플래시 메모리 유형 모두에 적용할 수 있는 세 가지 기본 연산(읽기, 쓰기, 지우기)

읽기/쓰기 단위는 페이지, 페이지 크기는 제품에 따라 1byte에서 2KB 등으로 고정되어 있음

지우기 작업의 단위는 블록으로, 이 블록은 여러 페이지로 구성되어 있으며, 블록 크기는 일반적으로 4KB에서 128KB 사이

NOR형 플래시 메모리의 경우 페이지 크기는 일반적으로 1byte이며, 이는 각 바이트를 개별적으로 읽고 쓸 수 있음을 의미

반면 NAND형 플래시 메모리는 대용량 스토리지에 더 최적화되어 있으며, 페이지 크기는 일반적으로 하드 디스크의 섹터 크기와 일치하는 512byte, 이것은 같은 페이지 내 각 바이트의 프로그래밍이 완전히 겹치기 때문에 NOR형 플래시 메모리에 비해더 큰 크기의 쓰기 대역폭을 제공

그러나 블록 장치 같은 형질 때문에 NOR형 플래시 메모리의 개별 바이트 프로그래밍 기능에 의존하는 초기 FTL 설계는 NAND형 플래시 메모리에 직접 적용이 불가능함

FTL 디자이너를 위해 NAND형 플래시 메모리는 일반적으로 예비 영역이라고 하는 각 페이지에 몇 byte의 관리 정보를 저장하는 추가 스토리지를 제공함

데이터가 사실상 오버헤드 없이 작성될 때 이 예비 영역을 동시에 작성할 수 있음

예비 영역은 또한 읽고 쓰는 동안 오류를 감지하기 위해 외부 논리에 의해 작성된 ECC 코드를 작성하는데 사용됨

이후 효율적인 대량 읽기/쓰기 작업 및 비교적 짧은 삭제 시간과 같은 대용량 스토리지로서의 우수한 특성 때문에 NAND형 플래시 메모리로 관심을 제한

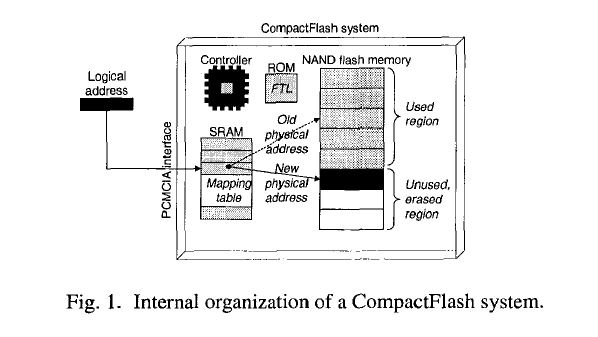

그림 1은 일반적인 NAND형 플래시 메모리 기반 CF의 내부 조직을 보여줌

하나 이상의 NAND 타입의 플래시 메모리 칩, ROM에 저장된 FTL 코드를 실행하는 컨트롤러, 주소변환과 관련된 데이터 구조를 저장하는 SRAM 그리고 호스트에 대한 인터페이스로 구성

호스트는 섹터 주소 및 요청 크기와 함께 하드 디스크 드라이브 같은 CF 시스템에 read/write 명령을 실행

명령, 주소 및 크기를 수신하면 FTL은 플래시 메모리 고유 명령(읽기/쓰기/지우기) 및 물리적 주소 순서로 변환

주소 변환은 SRAM에 저장된 매핑 테이블을 조회하여 수행되며, 처음에는 플래시 메모리의 예비 영역을 검사하여 구성

FTL은 각 쓰기 요청을 다은 위치에서 다시 매핑함으로써 플래시 메모리 제한을 수정하여 호스트에 투명하게(transparently) 덮어쓰지 못하도록 할 수 있음

논리 주소와 실제 주소간의 매핑은 페이지(쓰기 단위) 혹은 블록(지우기 단위) 수준에서 유지 관리한다.

--> 섹터 매핑을 말하는듯

페이지 수준 주소 매핑을 사용하면 논리적 페이지를 플래시 메모리의 모든 실제 페이지에 패밍할 수 있으므로 유연하게 관리가 가능하지만, 필요한 매핑 테이블을 저장하는데 많은 양의 SRAM이 필요로 함

예를 들어 페이지 크기가 512byte인 16MB 플래시 메모리 칩을 사용하는 CompactFlash 시스템에는 매핑 테이블에 64KB SRAM을 필요로 함

매핑 테이블의 크기는 플래시 메모리의 용량이 증가함에 따라 확장되며, 1GB CompactFlash 시스템의 경우 4MB의 SRAM을 필요로 함

--> 블록 매핑

블록 레벨 주소 매핑에서 논리 주소는 논리 블록 주소와 블록 오프셋으로 나뉘며, 논리 블록 주소만 매핑에서 플래시 메모리의 물리적 블록 주소로 변환 (블록 오프셋은 변환에서 불변)

블록 레벨 주소 매핑은 매핑된 물리적 블록의 블록 오프셋이 논리 블록의 블록 오프셋과 동일하다는 제한을 두지만, 훨씬 더 작은 매핑 테이블을 필요로 함

예를 들어 페이지 크기가 512byte이고 블록 크기가 16KB(32페이지)인 동일한 16MB CompactFlash 시스템은 매핑 테이블에 2KB SRAM을 필요로 함

대용량 플래시 메모리는 일반적으로 블록 크기가 크기 때문에 페이지 레벨 매핑(섹터 매핑)처럼 테이블의 크기가 선형적으로 증가하지 않음 -> 블록 크기가 128KB인 256MB 플래시 메모리 칩은 8KB의 SRAM만 필요

그러나 블록 레벨 주소 매핑은 쓰기 요청이 블록의 일부만 오면 일반적으로 추가 플래시 메모리 작업을 필요로 한다.

예를 들어, 단일 페이지에 대한 쓰기 요청이 있을 때마다 요청된 페이지를 포함하는 물리 블록이 빈 물리 블록에 다시 매핑되도록 동작

쓰기 작업은 동일한 블록 오프셋을 사용하여 새 물리적 블록의페이지에 수행되고, 동일한 블록의 다른 모든 페이지는 원래 물리적 블록에서 새 물리적 블록으로 복사가 필요함

--> M-systems (대체 블록)

이러한 값비싼 복사 작업을 제거하기 위해, 대체 블록에 기초한 기술이 제안됨

대체 블록 체계라고 불리는 기술은 블록의 기존 페이지에 덮어쓰기가 있을 때 교체 블록이라는 임시 블록을 할당하고 동일한 블록 오프셋을 사용하여 교체 블록의 페이지에 쓰기 작업을 수행

또한 페이지 중 하나를 다시 덮어쓸 경우 대체 블록 자체에 자체 대체 블록이 있을 수 있음

동일한 노리 블록에 속하는 이러한 교체 블록은 링크된 목록에 유지되고 읽기 및 쓰기 작업 모두에 대해 통과

읽기 작업의 경우, 교체 블록에서 가장 최신 페이지를 찾기 위해 통과되고, 쓰기 작업의 경우 교체 블록에서 동일한 블록오프셋을 가진 첫 번쨰 사용 가능한 페이지를 찾기 위해 이동

덮어쓰기 요청이 있고 사용 가능한 공간이 없을 때 모든 교체 블록의 최신 페이지를 하나의 블록으로 병합하고, 이것은 논리 블록을 나타내는 새로운 물리 블록이 된다.

이 병합 작업 후에는 이전 논리 블록과 대체 블록을 제외한 대체 블록이 지워지고, 다른 데이터 블록으로 대체 블록을 사용할 수 있는 자유 블록이 됨

- 참고 문헌 -

A SPACE-EFFICIENT FLASH TRANSLATION LAYER FOR COMPACTFLASH SYSTEMS

https://citeseerx.ist.psu.edu/viewdoc/download?doi=10.1.1.124.3802&rep=rep1&type=pdf

'개인 공부 > Flash Memory' 카테고리의 다른 글

| BAST (2021-02-18) (0) | 2021.02.18 |

|---|---|

| BAST (2021-02-17) (0) | 2021.02.17 |

| A survey of Flash Translation Layer (2021-02-11) (0) | 2021.02.11 |

| A survey of Flash Translation Layer (2021-02-09) (0) | 2021.02.09 |

| A survey of Flash Translation Layer (2021-02-08) (0) | 2021.02.08 |